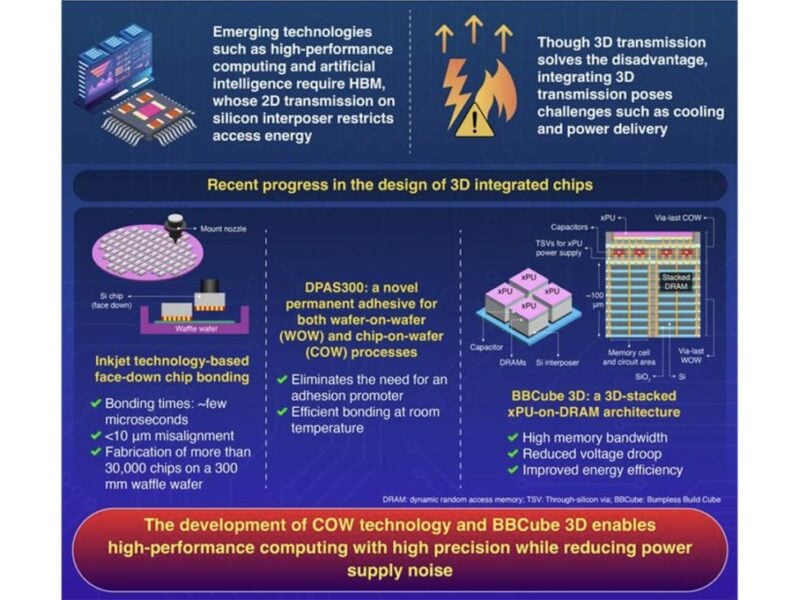

传统的体系级封装(SiP)办法,其间半导体芯片运用焊点摆放在二维平面(2D)上,存在尺度相关的约束,需求开发新的芯片集成技能。为了高性能核算,研讨人员经过选用 3D 堆叠核算架构开发了一种新式电源技能,该架构由直接堆叠的动态随机存取存储器上放置的处理单元组成,这是 3D 芯片封装的严重前进。

为了完成 BBCube,研讨人员开发了触及准确和高速键合技能和粘合剂技能的关键技能。这些新技能能协助满意高性能核算运用的需求,这些运用需求高内存带宽和低功耗,并削减电源噪声。

该研讨团队由小桥典雄教授、大庭隆之教授和来自日本东京科学研讨所(Science Tokyo)归纳研讨所的 WOW 联盟异构和功用集成部分的其他科学家组成,开始开发了一种倒装芯片-晶圆(COW)工艺,以躲避运用焊料互连的约束。使用喷墨技能和选择性粘合涂层办法,他们成功地将不相同的尺度的芯片顺次粘合到晶圆距离为 10 微米、最小装置负载时刻小于 10 毫秒的 300 毫米蛋挞状晶圆上。解说准确的 COW 工艺,小桥评论道:“在蛋挞状晶圆上制作了超越 30,000 个不相同的尺度的芯片,完成了更高的粘合速度,且没有一点芯片掉落毛病。”

为了完成准确高速的 COW 工艺,研讨人员专心于处理影响超薄晶圆多层堆叠的耐热性问题。经过精心设计化学特性,他们开发了一种新式粘合资料,称为“DPAS300”,该资料可用于 COW 和晶圆对晶圆工艺。这种新式粘合剂由有机-无机杂化结构组成,在试验研讨中表现出杰出的粘附性和耐热性。

最终,为完成高内存带宽并进步 BBCube 的电源完整性,科学家们选用了一种由新式电源分配高速公路强化的 3D xPU-on-DRAM 架构。这包含在 xPU 和 DRAM 之间嵌入电容器,在晶圆上施行重散布层,以及在晶圆通道和 DRAM 刻线中放置硅通孔。乔指出:“这些立异将数据传输所需的能量削减到传统体系所需能量的五分之一到二十分之一,一起还将电源噪声按捺到 50 毫伏以下”,突出了 3D 堆叠核算架构的优势。